Q. 5.1: The D latch of Fig. 5.6 is constructed with four NAND gates and an inverter. Consider the

16:44

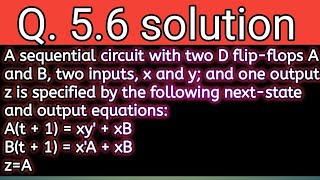

Q. 5.6: A sequential circuit with two D flip-flops A and B, two inputs, x and y; and one output z is

22:10

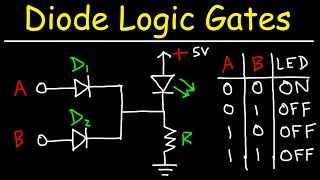

Diode Logic Gates - OR, NOR, AND, & NAND

4:40

Q. 5.2: Construct a JK flip-flop using a D flip-flop, a two-to-one-line multiplexer, and an inverter

9:42

I was asked to keep this confidential

32:20

JD Vance goes after European allies in Munich Security Conference speech | DW News

2:00:11

Candy Land Valentine's Day Relaxing Ambience | Lofi Music for Study & Focus

12:14

Latches and Flip-Flops 1 - The SR Latch

43:13