Q. 5.2: Construct a JK flip-flop using a D flip-flop, a two-to-one-line multiplexer, and an inverter

12:27

Q. 5.1: The D latch of Fig. 5.6 is constructed with four NAND gates and an inverter. Consider the

5:27

Q. 5.3: Show that the characteristic equation for the complement output of a JK flip-flop is Q'(t+1)

1:31

UNBOXED: POWERBOX65.4MDSP-V3

43:34

Q. 5.19: A sequential circuit has three flip-flops A, B, C; one input x_in; and one output y_out.

18:33

Kafka Tutorial for Beginners | Everything you need to get started

16:44

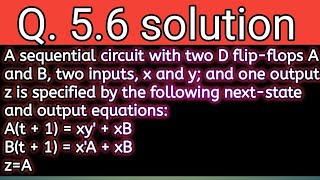

Q. 5.6: A sequential circuit with two D flip-flops A and B, two inputs, x and y; and one output z is

1:32:57

Week_3 Control Engineering_2025

12:17