Q. 5.1: The D latch of Fig. 5.6 is constructed with four NAND gates and an inverter. Consider the

4:40

Q. 5.2: Construct a JK flip-flop using a D flip-flop, a two-to-one-line multiplexer, and an inverter

16:44

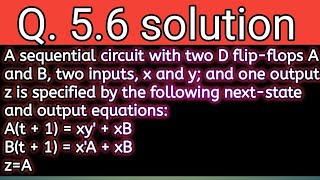

Q. 5.6: A sequential circuit with two D flip-flops A and B, two inputs, x and y; and one output z is

12:41

Q. 4.30: Using a decoder and external gates, design the combinational circui defined by the followin

22:47

2BIT ALU WITH MEMORY (RAM)

20:32

Let's Make A Screw Shortener

21:44

The real "User Error" is with Nvidia

22:22

Q. 6.9: Two ways for implementing a serial adder (A + B) is shown in Section 6.2. It is necessary

17:31