The Fetch Decode Execute Cycle

8:23

Pipeline Architecture

28:00

How do computers work? CPU, ROM, RAM, address bus, data bus, control bus, address decoding.

7:55

Fetch Decode Execute Cycle in more detail

9:04

The Fetch-Execute Cycle: What's Your Computer Actually Doing?

13:05

2. OCR A Level (H406-H466) SLR1 - 1.1 Fetch, decode, execute cycle

10:27

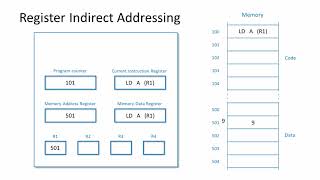

Processor Addressing Modes

16:07

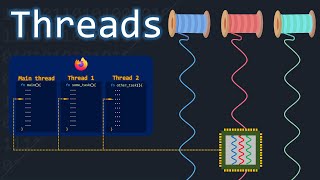

Why Are Threads Needed On Single Core Processors

29:31