Tutorial 15: Verilog code of 4_bit subtractor using full adder/ concept of Instantiation

5:11

Tutorial 16: Verilog code of 16_bit adder

20:10

Experiment 1.b || 4-bit adder and subtractor || Verilog Code, Working Explanation || #verilog

9:46

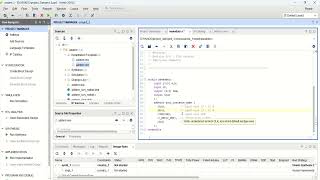

Tutorial 13: Verilog code of Full adder using using half adder/ Instantiation concept

20:38

4-bit Adder and Subtractor Circuit Explained

18:28

4-Bit Full Adder Design with IP Catalog in Xilinx Vivado.

26:44

[VHDL] Full Adder in Quartus using Two Half Adder with Port Map

14:50

The best way to start learning Verilog

10:04